適用分野半導体

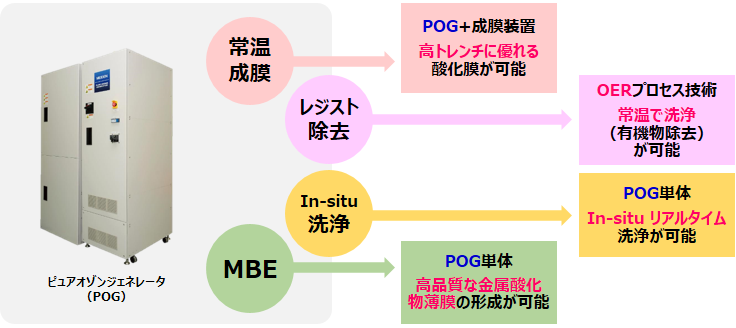

ピュアオゾンジェネレータは、半導体用途で様々なアプリケーションがあります。洗浄(In-Situ洗浄・アッシング)、成膜(高トレンチへの酸化膜)、MBE(分子線エピタキシー)の酸化源用途など多岐にわたる活用が可能です。

At semiconductor fields such as metal oxide semiconductor HEMT for 5G, and OLED, film deposition with pure ozone enables excellent step coverage by a superior diffusion capability of the ozone gas.

Also pure ozone can be used as a strong and high-purity oxidation source for MBE and ALD.

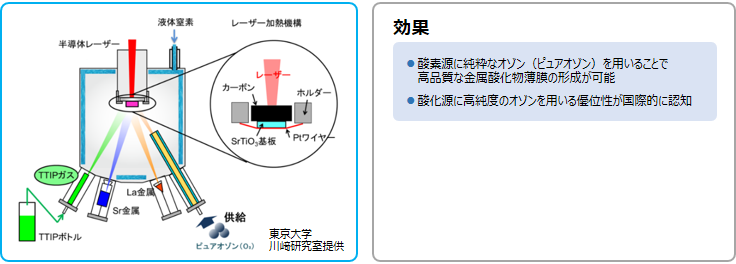

MBE(分子線エピタキシー)用の酸素源適用例

MBEに用いられる酸化源(通常は酸素を用いる)を高純度・高濃度オゾン(ピュアオゾン)に置き換えることで、高品質な金属酸化物薄膜を形成することができます。酸化源に当社の高純度・高濃度オゾンを用いる優位性に関しては、既に当分野の主要な国際的な大学でも数々の論文が発表されています。

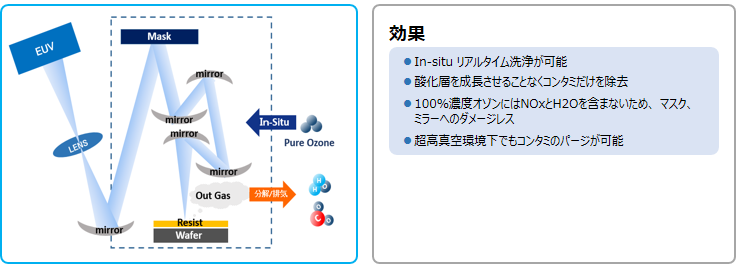

EUV露光装置の後工程のIn-situ洗浄適用例

半導体装置分野(EUV露光装置へのIn-Situ洗浄適用)でも、ピュアオゾンは優れた優位性を発揮します。ピュアオゾンの活性により、コンタミがマスク・ミラーに付着する前に、In-Situ洗浄で除去することが可能です。ピュアオゾンにはNOxとH2Oを含まない為、マスク・ミラーへもダメージを与えずに洗浄をすることができます。また超高真空環境下でも、コンタミのパージが可能です。

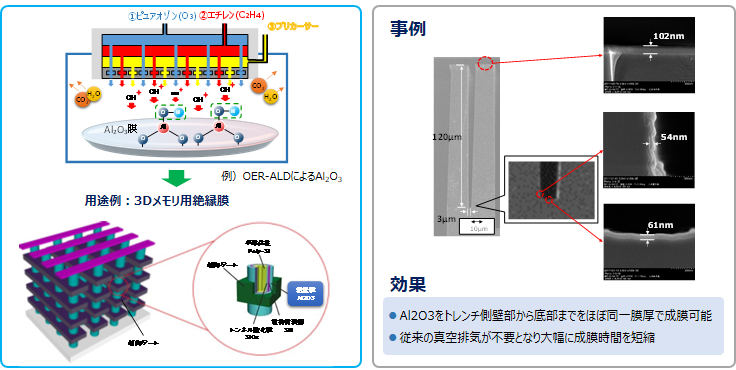

高トレンチ基板への適用例(アスペクト比 40:1)

当社のピュアオゾン(PO)、またはピュアオゾン+エチレン(OER)を用いた成膜技術では、高トレンチ基板に対しての成膜も低温・基材へダメージレスで行う事が出来ます。(実績:40:1の高アスペクト比)

下記の例では、アルミナ膜(AL2O3膜)をトレンチ側壁部~底部までほぼ同一膜厚、均一性を保ちながら成膜しています。また従来の真空排気が不要となり、大幅に成膜時間を短縮することができます。

用途としては3Dメモリ用絶縁膜用途等、様々なアプリケーションが考えられます。

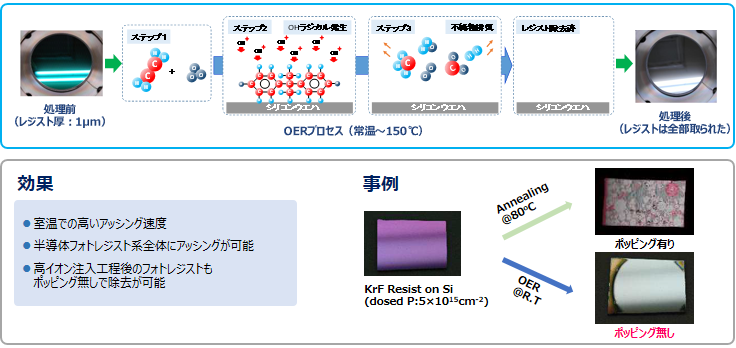

半導体製造工程(高イオン注入後)のレジストアッシング例

当社のピュアオゾン+エチレン(OER処理)の活性を利用し、ダメージレス・常温でのアッシングが可能となります。通常のアッシングでは除去しづらい高イオン注入工程後のフォトレジストも、ポッピング無しで除去が可能です。(下記写真参照)

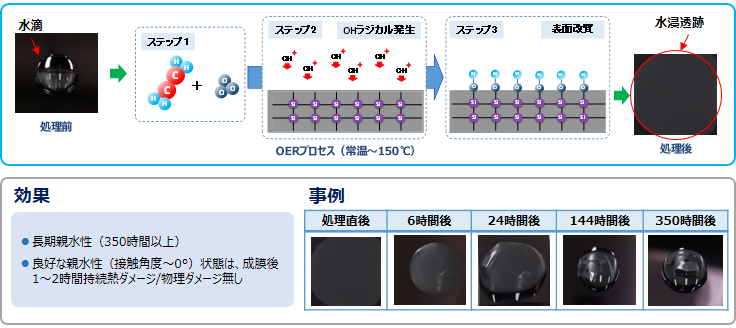

ピュアオゾンによる親水性向上例

OER処理では、様々な基材に長期親水性を持たせることができます。大量発生したOHラジカルが基材に入り込み、熱ダメージやプラズマダメージ無しで親水性を付与することが可能です。半導体分野に関しては、ガラス基板やシリコンウエハーへの応用も可能です。